| [目的] |

ロックインアンプの応答速度の高速化を目指す。

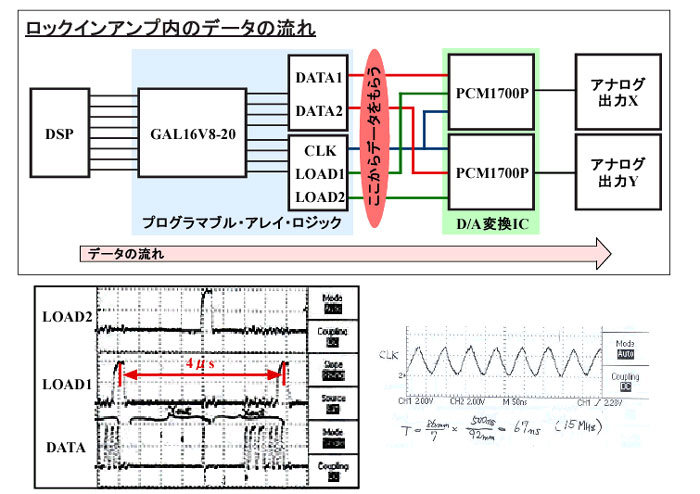

今回使用したロックインアンプはDSPロックインアンプであり。DSPとは、Digital

Signal Processor の略で、ディジタル信号を高速に処理するように設計されたプロセッサです。最大の特徴は、複数の処理を並列に実行可能な構造を持っていることです。内部構造を見ると、プログラムとデータに対してそれぞれ専用のメモリとバスを持っており、プログラムとデータの両方を同時に転送することができ、ハーバードアーキテクチャと呼ばれる構造を取っています。さらに演算器についても、信号処理で使用頻度の高い積算用と加算用の演算器が並列に実行可能な形で内蔵されています。

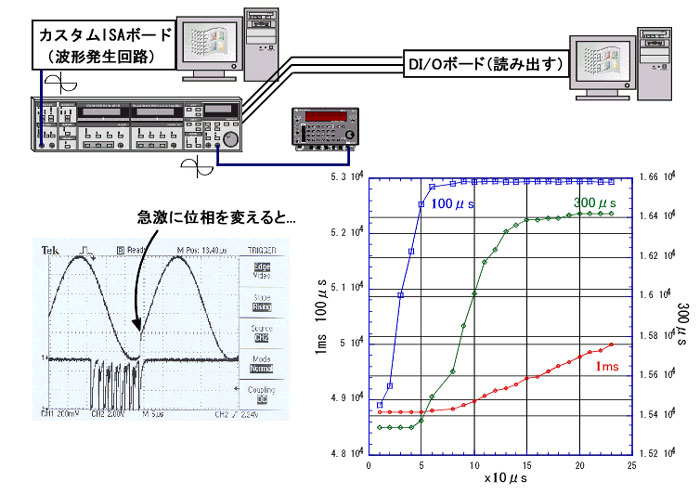

DSPロックインアンプの出力データの受け方としては、GPIBがあります。GPIBの信号の早さは、約33MSと遅くGPIBを使って実験を行うと時間がかかって仕方がありません。また、研究室のDSPロックインアンプには外部出力として電圧変換されて出てくる出力インターフェイスがあります(先生によると付録で付いているみたいです)。が、こちらも、あまり高速とはいえず、またアナログ出力であるがために誤差が多くなる可能性があります。他に方法は無いかと考えました。

DSPロックインアンプを使わずに自分たちで電気回路を作製してしまおうと考えたのが、益田、尾上班でこちらは300μsでデータを更新できる速度を持っています。僕たちはDSPロックインアンプを使い応答速度を益田、尾上班に負けないくらいの応答速度を実現できないかと考えました。 |